Professor

Department of Electronics & Telecommunication Engineering

A post graduate in Engineering from Mumbai University, Prof. Shiburaj P. is passionate about innovation & research. For him his work is of prime importance. Being a teacher he likes to guide his students in a proper direction to attain their goals in lives. His students describe him as creative, educated, intelligent, generous, noble & friendly.

ORCID: 0000-0002-6200-7270

ORCID: 0000-0002-6200-7270

Scopus Author ID: 56045838100

Scopus Author ID: 56045838100Department of Electronics & Telecommunication Engineering

Rizvi College of Engineering, Mumbai

Rizvi College of Engineering, Mumbai

Rizvi College of Engineering, Mumbai

Rizvi College of Engineering, Mumbai

SoftwareWorkshop.NET, Mumbai

Master of Engineering (E&TC)

Sardar Patel Institute of Technology, University of Mumbai.

Bachelor of Engineering (E&TC)

S.S.P.M. COE, University of Mumbai.

Recent trends in Soft Computing Techniques. Currently his research interest includes solution to problems which are NP-complete. He is also working on an innovative and secure mechanism to deliver images with emails.

Guide: Prof. S.G. Hate

Group Members: Jenniffer, Shiburaj, Prathamesh, Deepak, Pritesh

This project implemented an innovative concept of using wavelets to compress audio. Psychoacuostic model of the human ears and huffman coding to get a very high compression ration of 6:1.

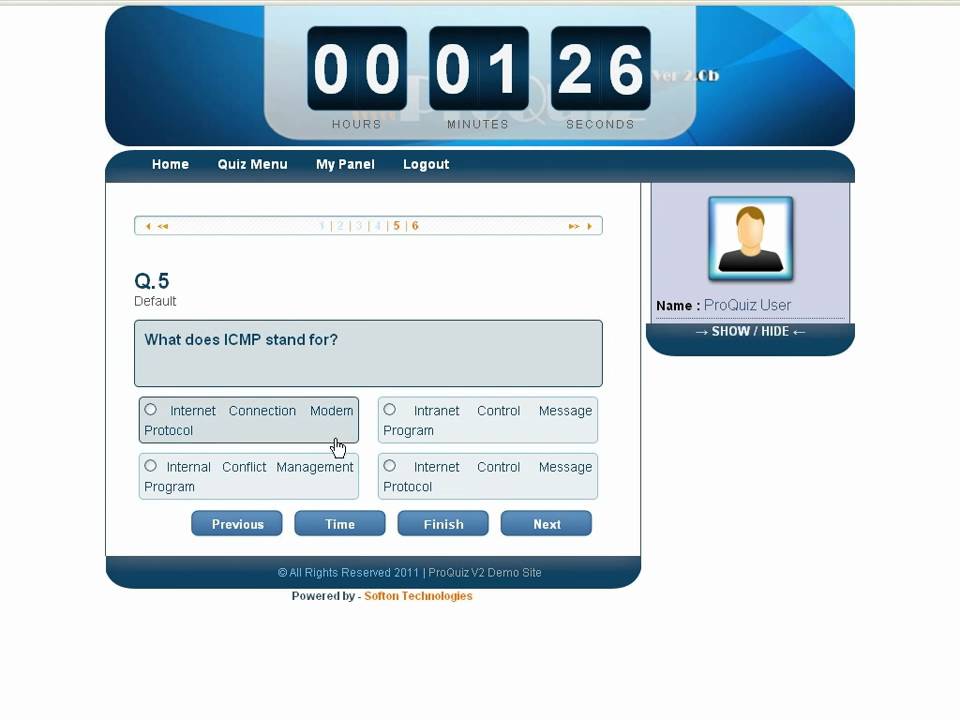

ProQuiz Ver 2.0.0 is a Professional Quiz Maker Software capable of Generating Quizzes of all types by simple user interface. Its easy User-friendly interface makes it stand apart from other softwares in this category.

This product provides a customized solution to super markets and shops as a stock management and ERP management. Clients: Om Super Market, Aufinja, Anja Jewellers and many more.

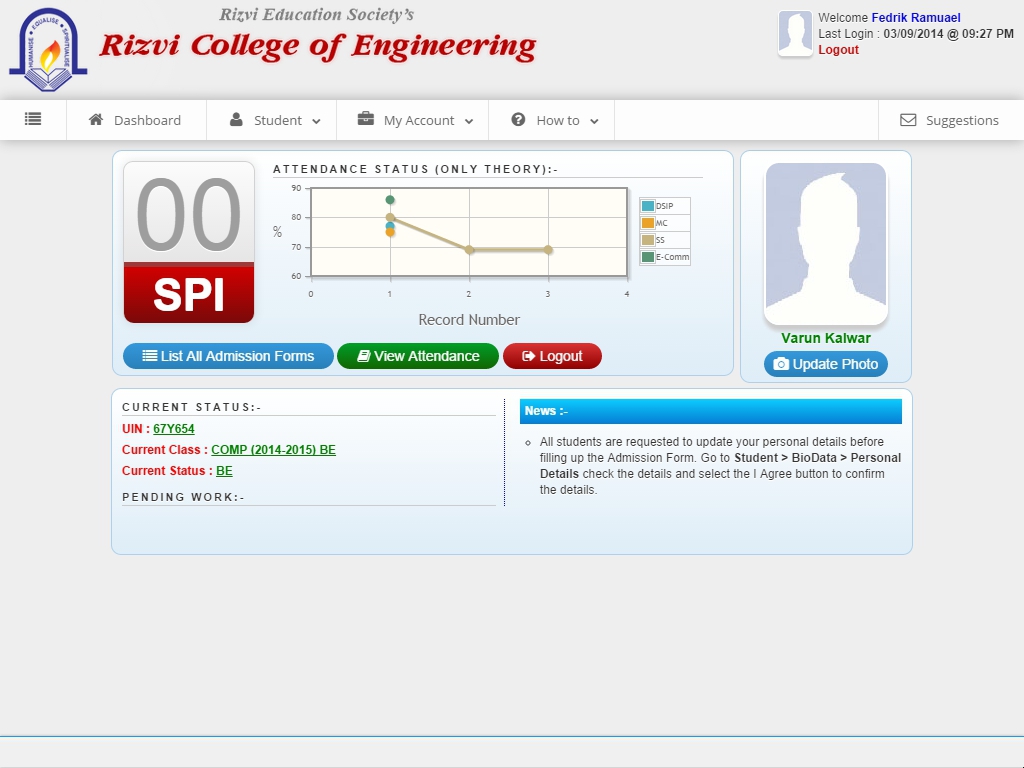

A complete college management system. From student admissions to Alumni management. Attendance record, Faculty & Student Activity & performance evaluator. and lots of other features.

Project Guide: Prof. K. T. Talele, SPIT, Mumbai.

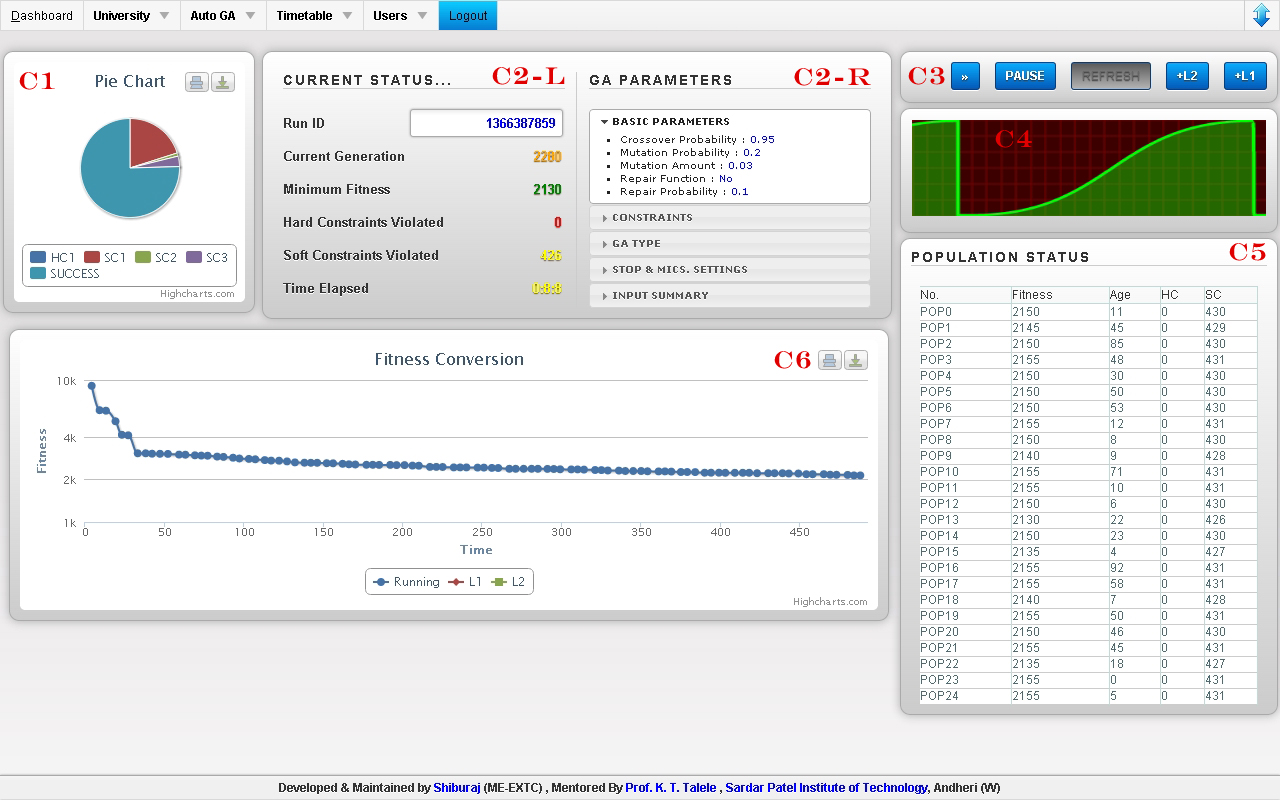

Scheduling oral exams timetable, for large number of courses and colleges within universities is a complex problem since it has to be solved by using traditional method which takes several days of iterative work. This project implements an effective solution to solve this problem by using Genetic Algorithm. An optimized timetable is produced which satisfies certain hard & soft constraints which distributes load to the examiners at the same time balancing the load amongst them and reducing the travel distance which in turn increases the usability of the generated schedule. The project implements two of the popular variants of genetic algorithm viz.: Steady State Genetic Algorithm (SSGA) & Enhanced Steady State Genetic Algorithm (ESSGA). The former is a special modification of the traditional genetic algorithm with only one pool for the process, while the later is an enhancement to SSGA which uses Fuzzy Logic to enhance the performance. After performing a set of tests using real data from several departments,subjects and colleges under the university, it is found that the ESSGA gains better timetable than other methods.

Some of my research papers in various Conferences & Journals.

This article describes various plotting algorithm and hence concludes the efficient algorithm which can be used to speed up the plotting process. Various graphical algorithms will be analysed and the best algorithm will speed up the plotting process adopted by various plotter. We will also have a look on the advantages and disadvantages of all the algorithms.

The growth of the gesture technology has accelerated very swiftly in recent years. The reason behind the fast evolution of gesture recognition is that it has its numerous applications in many fields and also it is potent to interact with machines via HumanComputer Interaction (HCI). In this paper, introduction to various gesture recognition technique and their drawbacks, application of this recklessly developing technology are mentioned. The key reasons and important points are mentioned to illustrate some algorithm’s efficiency in terms of complexity, time consumption, better output, fast responding, cost, etc. and to conclude the best among them. The intention of this work is to conclude the best and efficient approach of the implementation of the gesture recognition systems so that our society can be firm to implement the system by understanding its pros and cons and trusting upon the type of implementation they adopt for any of their purpose would be more beneficial for them in all aspects.

Dozens of people are suffer from temporary or permanent disabilities due to health issues or accidents. For cases of difficult, pain or impossible walking, the use of a power wheelchair is becoming really important. Manual or electrical wheelchairs do perform their work for most of the low and medium level disability cases. Though many disabled people stay satisfied with traditional manual or powered wheelchairs, there is a segment of disabled community which finds it difficult or impossible to use wheelchairs independently without any help. In such cases users often lack independent mobility. Researchers involved in medical industry are aiming at designing smart wheelchairs as viable solutions. Various wheelchairs have been created already. Many other wheelchairs have been created by using brain signals, vision dependence and head gestures. The undermined project is to design a smart wheelchair using voice recognition and an android application. The user can use it with comparatively less effort in an easy, independent and efficient manner.

With every passing day, mobile navigation is getting better and better. It all is useless though when we are riding a bike as the shaking bike will make it difficult for the phone to stay still. In order to overcome this problem, we introduce ‘The Navigation Belt’. The system consists of a belt with 4 directional vibrators fit in it. All these vibrators will be connected to an Arduino Nano chip which acts as the commander in the system. With the help of Bluetooth, it will receive directions on where to go and the vibrators will vibrate accordingly. Hence whenever the user wears a Navigation Belt each and every turn he has to take will be said to him via his vibrating belt, hence he won’t have to look at the phone and neither remember the directions for a complete journey.

Mobile phones are phenomenal in recent years for communication as well as in day-to-day life. Hence, charging the mobile phones has become the greater task. In this paper; we are trying to design a mobile battery charger on coin insertion. As uses of mobile phones are increasing day by day it need battery life all the time, so in order to use them public charging is needed which would be useful for mobile users. This system will charge the mobile phone for a particular time-period. When the valid coin is recognized, it will start giving power supply to the cell phone through one of the adapters. We will be using a global charging adapter that would be suitable for all mobile phones. The mentioned system can be implemented in public places like railway stations, bus stops, hospitals, malls, etc. to avail the services.

The Intel Core i5 4670K is a Haswell processor sporting four cores, each Over-clocked at 3.4GHz. What is new about the 4670K and differentiates it from its predecessor the i5 3570K is better power consumption, and it also offers better CPU performance, as well as improving on the GPU (Graphical Processor Unit), than the 3570K, which is a good gaming processor in itself. The processor is also capable of sustaining up to four different threads, promising good performance. Now the 4670K succeeds the 3570Kilobyte and enters the CPU charts as another great gaming processor.

Since the computer is invented the main heart of the computer is the CPU (performance). We have researched from the earlier paper that processor was not enough to compute with the performance. This paper, explains the characteristics of processor performance and its implementation for several configurations, Including Intel quad core processor, Quad-core multi-processor, Quad Core CPU Chip having 4 cores on one single chip, Thread-Level Parallelism. Using the clock rate, the CPU’s execution time, which is the total time the processor takes to process some program in seconds per program (total number of bytes), can be calculated. We propose a performance evaluation methodology affected by a benchmark test. Measuring of such systems performance becomes an important task for any system embedded design process.

This paper describes the next-generation Intels Xeons microprocessor designed for a broad range of highly power-efficient servers, codename Dunnington. The Dunnington processor has six cores (three core-pairs) integrated with large, dense, on-chip caches, and it delivers the dramatic power efficiency of Intel’s 45nm high-K metal gate process and the Intel Core 2 microarchitecture to server platforms. This processor implements a high bandwidth-dedicated interface from each of the three core pairs to the last-level cache (LLC) for the effective use of the inclusive LLC. With high functional integration, large cache size, and 1.9 billion transistors, the processor’s moderate server-class die size of 503mm2 is achieved by optimizing the floor plan and physical design. Thermal Design Power (TDP) limits of 50, 65, 90, and 130W. This processor will be the first part to employ core recovery techniques for reducing product cost.

In July 7 2019, AMD launched Ryzen 5 3600 processor. This processor was launched to provide better all-round performances like gaming, multitasking, exceptional speed etc. and intention of hitting market by lower price as compare to other processor companies. For example, its competitive processor intel-5 9600k is expensive as compare to ryzen 5 3600.

To increase the processor speed and its respective performance a more streamlined method of approach was required. Electronic Design Automation (EDA) is implemented. This article describes the changes brought about by EDA in the development of microprocessor systems and the challenges faced by EDA currently and in the future. This article will also describe the various tests and experiments conducted on the CUDA architecture based microprocessor and also highlight the overall performance and thermals of the system under such extreme test conditions.

In this research paper, we will look at the Intel’s latest processor (1065G7). We will also deeply study the improvements and enhancement that have been introduced in his processors. For this I have gone through several papers and articles. We have found that this processor is rather fast and power-efficient and It is a very reliable processor and it is one of the best processors at this price range.

A microcontroller can be considered a self -contained system with a processor ,memory and peripherals and can be used as an embedded system .The majority of microcontrollers in use today are embedded in other machinery, such as automobiles , telephones , appliances and peripherals for computer systems .Mixed signal microcontrollers are common integrating analog components needed to control non digital systems In the context in the internet of things, microcontrollers are economical and popular means of data collection, sensing and actuating the physical world as edge devices.

In the microprocessor industry we see that energy efficiency is one-off the main issues that we are faced with.The motivation for our paper is the increased applications which use embedded systems for communication and multimedia. In our paper you will see the changes in techniques that have made a considerable amount of development to make sure that the efficiency of the microprocessor consumes will be less but also not compromise with the performance (clock speed) that it provides to the users. Internet connectivity has caused the devices to be in use all day long because of this the rate at which the microprocessor runs uses great amount of energy because of which energy efficiency has to be good. Ever since caches were introduced they present the most attractive ways for power reduction. To implement coherent caches using MESI protocol we use snoop filtering mechanism.

Intel has launched a 32bit microprocessor which was designed for high performance and to drive the most advanced computer-based applications. The 80386 offers the system designer many new and powerful capabilities, including unprecedented performance of 3 to 4 million instructions per second. The addressing modes of 80386 support efficient access to the elements of the standard data structures.

Satellite images are multispectral or hyperspectral images, which are important for earth observation and military reconnaissance. However, there exists big incompatibility between the transmission capacity of satellite channel and large amount hyper spectral data. There are spatial and spectrum redundancy in hyper spectral image. As to exploit spectrum correlation sufficiently, it must be to pre-process hyper spectral image. In this paper, we propose a novel acceptable complexity lossy hyper spectral image compression scheme. Conventional approaches to sampling signals or images follow Shannon’s celebrated theorem, which says that the sampling rate must be at least twice the signal bandwidth (the so-called Nyquist rate). In fact, this principle underlies nearly all signal acquisition protocols used in consumer audio and visual electronics, medical imaging devices, radio receivers, and so on. Compressive sampling, also known as compressed sensing or CS, a novel sensing sampling paradigm that goes against the common wisdom in data acquisition. CS theory asserts that one can recover certain signals and images from far fewer samples or measurements than traditional methods used. Keywords: Image compression; compressive sensing (CS); sparsity; discrete cosine transform (DCT); isometry; orthogonal pursuit matching(OMP).

Optimization problems like Exam Timetabling Problems (ETTP) are a complex set of NP-Hard problems, solutions to which by using traditional methods may be impossible or time consuming. We describe an effective solution to solve this problem by using multiple instances of a special form of Genetic Algorithm named Enhanced Steady State Genetic algorithm (ESSGA) running in parallel. The main drawback of using any variant of genetic algorithm is its convergence time to obtain optimal solutions. In this paper we propose and implement a parallel system for executing the genetic algorithms to yield optimal solution in less time.

Exam Timetabling Problems (ETTP) are a complex set of NP-Hard problems, solutions to which by using traditional methods may be impossible or time consuming. We describe an effective solution to solve this problem by using different form of Genet ic Algorithms like Steady State Genetic algorithm (SSGA), Simple Genetic Algorithm (SGA) and Generation Genetic Algorithm (GGA) running in parallel in a distributed nature. The main drawback of using any variant of genetic algorithm is its convergence time to obtain optima l solutions. In this paper we propose and implement a parallel system for executing the genetic algorithms to yield optimal solution in less time.

There exists big incompatibility between the transmission capacity of satellite channel and large amount hyper spectral data. There are spatial and spectrum redundancy in hyper spectral image. As to exploit spectrum correlation sufficiently, it must be to pre-process hyper spectral image. In this paper, we propose a novel acceptable complexity lossy hyper spectral image compression scheme. Conventional approaches to sampling signals or images follow Shannon’s celebrated theorem, which says that the sampling rate must be at least twice the signal bandwidth (the so-called Nyquist rate). In fact, this principle underlies nearly all signal acquisition protocols used in consumer audio and visual electronics, medical imaging devices, radio receivers, and so on. Compressive sampling, also known as compressed sensing or CS, a novel sensing sampling paradigm that goes against the common wisdom in data acquisition. CS theory asserts that one can recover certain signals and images from far fewer samples or measurements than traditional methods used.

Satellite images are multispectral or hyperspectral images, which are important for earth observation and military reconnaissance. However, there exists big incompatibility between the transmission capacity of satellite channel and large amount hyper spectral data. There are spatial and spectrum redundancy in hyper spectral image. As to exploit spectrum correlation sufficiently, it must be to pre-process hyper spectral image. In this paper, we propose a novel acceptable complexity lossy hyper spectral image compression scheme. Conventional approaches to sampling signals or images follow Shannon’s celebrated theorem, which says that the sampling rate must be at least twice the signal bandwidth (the so-called Nyquist rate). In fact, this principle underlies nearly all signal acquisition protocols used in consumer audio and visual electronics, medical imaging devices, radio receivers, and so on. Compressive sampling, also known as compressed sensing or CS, a novel sensing sampling paradigm that goes against the common wisdom in data acquisition. CS theory asserts that one can recover certain signals and images from far fewer samples or measurements than traditional methods used.

Optimization problems like Exam Timetabling Problems (ETTP) are a complex set of NP-Hard problems, solutions to which by using traditional methods may be impossible or time consuming. We describe an effective solution to solve this problem by using multiple instances of a special form of Genetic Algorithm named Enhanced Steady State Genetic algorithm (ESSGA) running in parallel. The main drawback of using any variant of genetic algorithm is its convergence time to obtain optimal solutions. In this paper we propose and implement a parallel system for executing the genetic algorithms to yield optimal solution in less time.

Scheduling & Optimization problems are iterative in nature. To find a ideal solution to which is a complex task. These types of problems may be effectively solved and optimal solutions which may be close to the ideal solution may be derived with the help of evolutionary algorithms like the Genetic Algorithm. This paper introduces a new variant of genetic algorithm called Modified Enhanced Steady State Genetic Algorithm (MESSGA) which uses Fuzzy Logic on crossover probability, mutation probability and insertion, for better convergence time. The results of this paper are studied on a common scheduling problem faced by all universities to assign externals for viva-vose or examination to other colleges under its jurisdiction.

His area of specialization and subjects taught in his teaching career. And some of his Technical Skills

This subject gives an overview of the concepts and fundamentals of data communication and computer networks. Exposes students to the TCP/IP protocol suite. Various routing protocols & Network Designing.

This subject introduces to the Technical aspect of Internet Technology and Advanced web programming. Study of various internet protocols, distributed computing and internet security are some of the topics covered.

Introduction to HTML5, CCS3, Javascript, XML & PHP.

Basic of Telecommunication. GSM & CDMA standards. GPRS & EDGE Networks.

Various processing techniques of Digital Signals. Z Transform & Fourier Transform. DFT & FFT. Filter Design.

Basics of Signals & Systems. Frequency Representation & Analysis of Analog Signals. Analog Filter Designs.

In depth study of Networking Protocols like ATM, SONET, X.25, Frame Relay etc. Unicast & Multicast Routing Protocols.

You can find me at my lab located at Rizvi College of Engineering, Off Carter Road, Bandra(W), Mumbai 400050. Lab 407 (4th Floor).

I am available in the lab every day from 9:30 AM to 3:30 PM.